普迪飞(PDF Solutions)用户大会上,来自爱德万(Advantest)、泰瑞达(Teradyne)的行业专家与普迪飞同台,围绕半导体先进测试的实际落地案例展开分享与交流,通过具体应用场景详解人工智能与机器学习在测试流程中的创新应用,拆解技术落地的核心要点与行业未来探索方向,以下为本次大会核心内容回顾。

90%置信度预判终测失效,降低高成本封装损耗

泰瑞达(Teradyne)Eli Roth

泰瑞达测试产品经理Eli Roth带来机器学习(ML)与高级分析结合的终测(Final Test)失效预测案例,直击晶圆分选(Wafer Sort)合格但终测失效导致封装成本浪费的行业痛点,详解技术方案与落地价值。

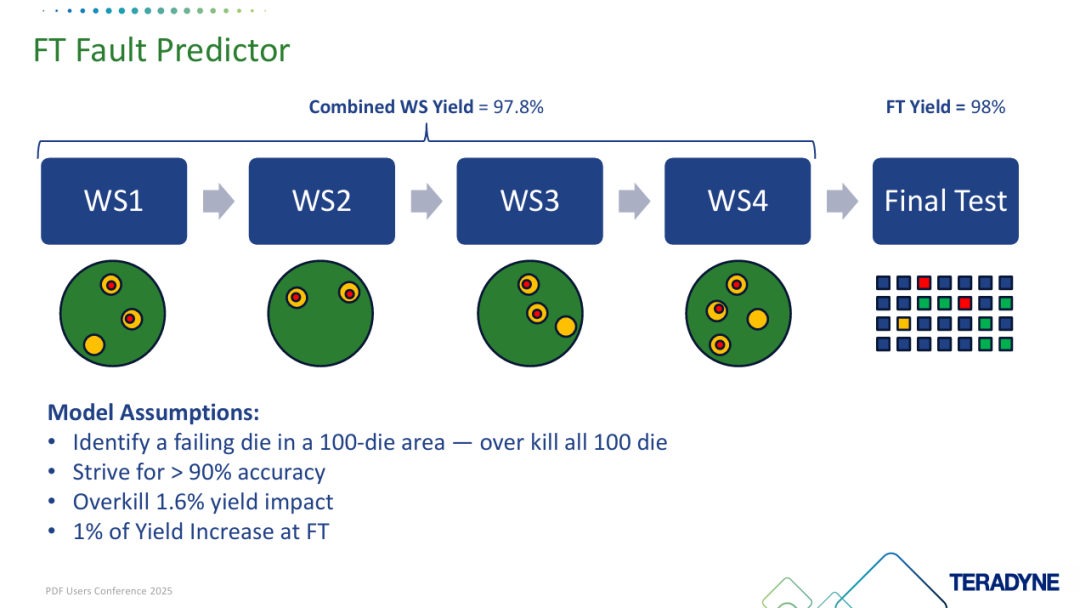

本次案例针对一款需完成四次冷热温循晶圆分选的器件展开,该客户原有产品良率与性能表现已处于较好水平,核心诉求是进一步提升终测良率,规避高成本封装环节的无效投入。为解决这一问题,泰瑞达团队开发多款机器学习模型,通过聚类算法(Clustering Algorithm)分析晶圆分选海量数据,建立模型置信度评估体系,以此预测芯片终测结果;经持续优化,模型识别缺陷芯片的置信度最终达到90%,可精准锁定终测易失效的高风险芯片集群。

在成本与收益的平衡上,团队通过经济测算综合权衡,以1.6%的晶圆分选“过杀率(Overkill Rate)”为代价,实现了终测良率1%的显著提升,该技术在芯粒(Chiplet)应用、已知合格芯片(KGD)等高价值领域,及封装成本居高不下的场景中具备显著经济价值。同时该方案落地性极强,适配客户已定型且不可修改的高产量量产测试程序,无需改动量产程序、无需重新认证,也不会打乱现有测试流程,即可实现良率提升与成本优化。

此外,该模型可与普迪飞Exensio平台集成,借助平台的模型重训练、机器学习管线搭建能力,及边缘计算(Edge Computing)技术支持,能在晶圆分选环节更快做出芯片分档决策,甚至省去不必要的晶圆分选测试步骤;模型部署形式灵活,可在主机运行、离线操作,也能在量产测试中在线运行,且支持整合所有测试环节数据进行分析,挖掘更多应用可能性。

针对本案例的现场问答

Eli Roth分享结束后,现场围绕模型搭建、落地挑战、客户后续规划等问题展开针对性提问,核心问答内容如下:

1

建模过程中是否剔除芯片数据及环节?

该终测失效预测模型最初基于晶圆分选与终测的一对一关联关系设计,本案例并未在各测试环节单独剔除芯片数据,而是借助四次晶圆分选的结果叠加分析,实现了更高的预测精度,这一方式让模型表现超出了通用模型的预期效果,也是本案例的核心优势。

2

除算力基础设施外,技术落地是否还有难点?

除搭建算力基础设施支撑运算外,数据囤积与数据安全是核心难点,获取客户信任让企业接触核心数据、保障数据安全、设置专属的数据访问权限体系,这些问题的解决难度甚至高于模型搭建本身;同时技术落地不仅是技术挑战,更是人类的挑战,本次合作是泰瑞达与客户的一对一合作,而多方利益相关方的参与会让问题复杂程度呈指数级上升。

3

该案例客户是否有后续的技术应用规划?

该客户明确希望将该预测技术应用于封装成本更高的产品上,本次案例中封装成本的节省与晶圆分选过杀带来的成本基本持平,而半导体行业的保守性决定了客户会优先寻找能产生明显正向投资回报的应用场景。本次落地项目将作为后续优化方案的试点,为技术打磨打下基础,同时该技术针对数字器件、数据中心专用器件、大尺寸器件等领域的行业痛点,具备广泛的应用空间。

Vmin智能优化技术,兼顾功耗降低与测试时间缩短

爱德万测试(Advantest)Roberto Colecchia

爱德万专家带来最小工作电压(Vmin)优化技术的应用分享,针对性解决传统Vmin测试精度与效率难以兼顾的行业痛点,为电池供电设备、高性能计算(HPC)领域的测试优化提供解决方案。

Vmin测试的核心目标是找到芯片无错误稳定运行的最低工作电压,传统测试方式需对每个芯片核心的供电电压进行扫频测试,虽能精准定位Vmin,但因需为每个核心重复执行搜索算法,会大幅增加测试时间;而若为芯片所有核心统一设定Vmin,又会造成不必要的功耗浪费。

机器学习技术为这一矛盾提供了解决方案:通过优化Vmin搜索窗口,借助机器学习推理预测每颗芯片、每个核心的潜在最小工作电压,大幅缩小电压搜索范围,在保证精度的同时显著节省测试时间;同时,为每个核心单独优化最优Vmin,能大幅降低芯片整体功耗,这一特性对电池供电的移动设备及高性能计算领域均具有重要价值。

该技术可在晶圆分选与终测环节落地,其规模化应用需具备三大核心要素:

1

实现跨测试环节的数据前馈,将前序测试数据同步至后续环节,为测试提供精准参考;

2

搭建边缘计算架构,将推理任务卸载至测试设备附近的服务器,保障实时推理与Vmin搜索计算效率;

3

部署云端解决方案,实现模型云端训练、现场快速部署,同时将测试结果反馈至云端,完成模型重训练与优化,实现量产过程中的模型持续迭代。

目前该技术在电池供电设备与高性能计算领域需求旺盛,已成为行业核心的测试优化方案。

针对本案例的现场问答

爱德万专家分享结束后,现场围绕技术落地实操、难点、未来探索方向等问题展开针对性提问,核心问答内容如下:

1

技术在实际量产落地过程中遇到的核心挑战是什么?

技术落地难度核心取决于客户现有的基础设施水平,若客户拥有端到端的基础设施,能实现云端、测试现场服务器与测试设备的互联互通,落地过程会非常顺畅;若客户仅有基础边缘计算方案,且模型更新需人工操作,无法实现实时更新,只能定期批量更新,落地难度会大幅增加。同时,为跨场地运营的客户落地该技术,会进一步增加问题的复杂性。

2

预测缩小Vmin搜索窗口时,核心参考哪些参数?

Vmin优化模型可挖掘利用数十万个参数,其中静态工作电流(IDDQ) 是核心参数,会对芯片不同模块的电流进行大量测量,为预测提供关键参考;同时还需整合其他芯片级数据,包括电压测量数据、前序测试环节的电流与电压数据,及同一测试环节中不同模块的测试数据等。

3

是否有企业对该技术的收益进行量化测算?

该技术的核心收益体现在芯片功耗降低上,功耗降低可节省电量、延长电池续航,企业也可因此提升产品溢价、获得更高利润,同时测试时间的缩短也能降低生产成本,只要选对应用场景,该技术能实现双赢,是降本提质的优质方案。

4

大规模多站点测试程序中,如何优化Vmin测试的吞吐量?

目前在大规模多站点测试程序中,存在部分站点吞吐量提升、部分站点仍速度较慢的问题,多站点Vmin测试的吞吐量优化,仍是该技术现阶段需要攻克的核心难题。

5

5.该技术后续的核心探索方向是什么?

Vmin优化技术的应用边界将向左移测试(Shift Left)延伸,不再仅仅聚焦于降低芯片功耗,还会通过分析早期测试数据,找到与后续芯片报废相关的关联规律,提前发现失效风险,进一步降低生产损耗。

现场观众提问环节

关于技术拓展与平台支撑相关问题

两位嘉宾完成案例分享与针对性问答后,现场观众围绕技术跨行业应用、芯片性能延伸、普迪飞平台支撑能力、模型管理部署等问题展开通用提问,嘉宾逐一详细解答,核心内容如下:

1.终测失效预测与Vmin优化技术,是否可应用于射频(RF)行业?

本次分享的两个模型均未针对射频器件开发,但市场上已有企业将类似方法应用于射频器件测试;Vmin优化技术的核心是基于搜索的应用方案,可适配射频测试中寻找最优工作频率等包含搜索环节的高频射频测试场景,利用晶圆分选数据预测射频测试结果,具备可观的应用价值。

2.低Vmin芯片在传统标准额定Vmin下运行,是否能提升使用寿命?

目前暂无明确答案,要验证这一问题,需开展芯片全生命周期的可靠性测试,这也是一项极具价值的实验;普迪飞数据前馈解决方案中设计的保留组功能或可解答该问题,该功能通过专门字段标记部分器件、晶圆或批次,其数据仅用于下游模型验证不参与训练,且对该部分芯片执行标准测试程序,可通过对比机器学习推理测试与标准测试的芯片,分析其使用寿命差异。

3.本次案例模型是否基于普迪飞Exensio平台搭建?

本次案例模型采用定制化方案完成落地,而普迪飞Exensio平台作为面向半导体测试行业的标准化智能平台,已规划内置模型漂移检测、自动重训练等核心能力,相关功能即将正式上线。当前行业内同类解决方案多为企业针对单一需求搭建的零散定制化方案,而Exensio平台凭借可扩展的标准化架构,将彻底解决这一行业痛点,为这类先进测试场景提供更高效、可复用的技术底座。

4.检测到模型漂移后,重新部署的难度及平台应对方案是什么?

AI模型需定期重训练与更新,重新部署的难度主要取决于所使用的平台;Exensio AI Studio平台已搭建面向公共的容器仓库,可对接任意云服务商,模型更新后可上传至该仓库,再下发至各远程测试现场完成部署,该过程依托容器编排技术实现,技术难度较低。

模型部署的核心难点在于配置管理,需精准记录每颗芯片对应的模型版本、跟踪全流程的数据血缘,同时还需满足行业合规要求,实现测试方法的长期追溯,而Exensio平台的一体化解决方案,能更好地解决此类问题。

数据协同成关键,技术仍处于初期探索阶段

核心观点

本次大会中,各位嘉宾围绕AI赋能半导体测试形成诸多行业共识,为技术后续应用与探索指明方向:

数据前馈与数据协同是测试优化的核心

此前行业内关于数据前馈的探讨多为假设性内容,如今相关解决方案已具备实际落地可行性,甚至可在跨地域的多场地运营场景中实现;整合各类测试环节的数据,不仅能优化芯片测试流程,还能为异构集成封装提供助力,实现更优的芯片匹配,提升芯片性能、降低功耗,甚至为异构集成器件提供分级依据。

AI与机器学习在半导体测试领域仍处于发展初期

目前行业内各团队均在尝试使用相关模型,探索其最佳应用场景,其中数据前馈是现阶段最具价值的应用方向之一;当前相关技术工具与算力已基本具备,行业可进一步探索更多提升良率、缩短测试时间、提高芯片产品利润的新方法。

芯片匹配(Die Matching)是行业下一阶段重点探索方向

芯粒封装中的芯片匹配技术,若能实现芯片最优匹配,可有效避免多芯片封装中良率的乘数效应损耗,虽目前暂无具体落地案例,且存在一定技术难点,但相关技术研究一直在持续推进,整个行业均在为之努力。

推荐阅读: